DESIGN

1. Tujuan [Kembali]

- Mempelajari cara mencari hambatan yang tidak diketahui yang dilengkapi JFET N-Chanel

- Mempelajari cara mencari hambatan yang tidak diketahui yang dilengkapi MOSFET N-Chanel

2. Alat dan Bahan [Kembali]

· Resistor

Resistor adalah komponen yang menyuplai hambatan yang digunakan untuk mengatur arus dan tegangan listrik.

· Ground

Definisi grounding adalah sistem pentanahan yang berfungsi untuk meniadakan beda potensial sehingga jika ada kebocoran tegangan atau arus akan langsung dibuang ke bumi.

· Voltmeter dan Amperemeter

Voltmeter adalah perangakat listrik yang berfungsi untuk menghitung tegangan dan amperemeter adalah perangkat yang berfungsi untuk menghitung arus yang mengalir di suatu rangkaian.

· JFET N-Chanel

JFET adalah transistor efek medan gerbang

persimpangan. Transistor normal adalah perangkat yang dikendalikan arus yang

membutuhkan arus untuk biasing, sedangkan JFET adalah perangkat yang

dikendalikan tegangan.

JFET N-Chanel

Saat Gate diberi tegangan 0 Volt maka depletion layer pada sambungan P-N pada pada kedua sisi tidak mengembang atau tipis sehingga arus dapat melintas dari Drain ke Source dengan mudah sehingga dapat mengalirkan arus. Semakin besar tegangan negatif pada terminal Gate maka depletion layer semakin lebar hingga maksimum dimana akan menutupi atau menghalangi jalur arus dari Drain ke Source sehingga tidak akan ada arus yang mengalir pada Drain atau JFET bisa dikatakan pada kondisi off.

· MOSFET N-Chanel

MOSFET (Metal Oxide

Semiconductor Field Effect Transistor) adalah sebuah perangkat semionduktor

yang secara luas di gunakan sebagai switch dan sebagai penguat sinyal pada

perangkat elektronik. MOSFET adalah inti dari sebuah IC ( integrated Circuit )

yang di desain dan di fabrikasi dengan single chip karena ukurannya yang sangat

kecil.

MOSFET N-Chanel

Struktur N-Channel Mosfet atau disebut dengan

NMOS terdiri dari subtract tipe P dengan daerah Source dan Drain deberi Difusi

N+. Diantara daerah Source dan Drain terdapat sebuah celah sempit dari subtract

P yang di sebut dengan channel yang di tutupi oleh isolator yang terbuat dari

Si02

3. Dasar Teori [Kembali]

Proses desain adalah fungsi dari area aplikasi, tingkat

amplifikasi yang diinginkan, kekuatan sinyal, dan kondisi operasi. Langkah

pertama biasanya adalah menetapkan dc yang tepat tingkat operasi.

|

Gambar 7.50 Konfigurasi bias diri untuk dirancang |

Sebagai contoh, jika tingkat

VD dan ID ditentukan oleh jaringan pada Gambar 7.50, tingkat VGSQ dapat ditentukan dari plot kurva transfer

dan Rs kemudian dapat ditentukan dari VGS = ID.RS. Jika VDD ditentukan, tingkat RD kemudian dapat dihitung dari RD (VDD - VD) / ID. Tentu

saja, nilai RS dan RD mungkin

bukan nilai komersial standar, yang mengharuskan penggunaan nilai komersial

terdekat. Namun, dengan toleransi (kisaran nilai) yang biasanya ditentukan

untuk parameter jaringan, sedikit variasi karena pilihan nilai standar jarang

menimbulkan kekhawatiran nyata dalam proses desain.

Di atas hanyalah satu

kemungkinan untuk fase desain yang melibatkan jaringan pada Gambar 7.50. Ada

kemungkinan bahwa hanya VDD dan

RD yang ditentukan bersama dengan tingkat VDS. Perangkat yang akan digunakan mungkin harus

ditentukan bersama dengan tingkat RS. Tampaknya logis bahwa perangkat yang dipilih harus memiliki

VDS maksimum yang lebih besar dari nilai yang

ditentukan dengan margin aman.

Secara umum, ini merupakan

praktik desain yang baik untuk amplifier linier untuk memilih titik operasi

yang tidak memenuhi wilayah tingkat saturasi (IDSS) atau batas (VP). Tingkat VGSQ yang mendekati VP / 2 atau IDQ di dekat IDSS / 2 tentunya merupakan titik awal yang masuk akal dalam

desain. Tentu saja, dalam setiap prosedur desain tingkat maksimum ID dan VDS sebagai yang muncul di lembar spesifikasi tidak boleh

dilampaui.

Contoh yang harus diikuti

memiliki orientasi desain

atau sintesis di tingkat tertentu yang disediakan dan parameter jaringan

seperti RD, RS, VDD, dan seterusnya, harus ditentukan. Bagaimanapun, pendekatan

ini dalam banyak hal berlawanan dengan yang dijelaskan di bagian sebelumnya.

Dalam beberapa kasus, ini hanya masalah penerapan hukum Ohm dalam bentuk yang

sesuai. Secara khusus, jika tingkat resistif diminta, hasilnya sering diperoleh

hanya dengan menerapkan hukum Ohm dalam bentuk berikut:

Dimana VR dan IR seringkali merupakan parameter yang dapat ditemukan langsung dari tingkat tegangan dan arus yang ditentukan.

4. Rangkaian [Kembali]

5. Video [Kembali]

6. Soal [Kembali]

1. Berdasarkan jaringan

Gambar 7.51, tingkat VDQ dan IDQ ditentukan.

Tentukan nilai RD dan RS yang

dibutuhkan. Apa nilai komersial standar terdekatnya?

Solusi

:

Seperti pada persamaan R :

Dari kurva transfer pada Gambar 7.51 dan menggambar garis horizontal pada IDQ =

2.5 mA akan menghasilkan VGSQ = -1 V, dan

menerapkan VGS = - IDRS akan

menetapkan tingkat Rs:

Nilai komersial standar terdekat adalah :

2. Untuk konfigurasi

bias pembagi tegangan pada Gambar 7.53, jika VD =12

V dan VGSQ = - 2 V, tentukan nilai

RS.

Solusi

:

Nilai VG yang

ditentukan sebagai berikut :

Persamaan untuk VGS kemudiann ditulis

dan nilai yang diketahui diganti :

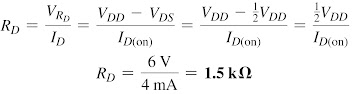

3. Jika VDS =

1/2 VDD and ID =

ID(on) untuk jaringan Gambar. 7.54 .

Tentukan tingkat VDD dan RD

.

Solusi :

Diberikan ID = ID(on)

= 4 mA dan VGS = VGS(on)

= 6 V, untuk konfigurasi ini :

Dengan persamaan dari

hasil (7.42) diperoleh nilai komersial standar :

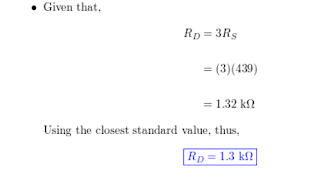

- Rancang jaringan self-bias

menggunakan transistor JFET dengan IDSS =

8 mA dan VP = - 6 V agar

memiliki Q-point pada IDQ =

4 mA menggunakan supply 14 V. Asumsikan RD =

3RS dan gunakan

nilai standar.

Jawab

- Rancang jaringan bias pembagi

tegangan menggunakan MOSFET tipe deplesi dengan IDSS 10

mA dan VP 4 V untuk

memiliki titik-Q pada IDQ 2,5

mA menggunakan suplai 24 V.Selain itu, atur VG 4

V dan gunakan RD 2.5 RS dengan

R1 22 M. Gunakan nilai standar.

Jawab

· Apakah kepanjangan dari JFET

a. Junction Field Effort Transistor

b. Jumper Field Effect Transistor

c. Junction Field Effect Transistor

d. Jumping Field Effect Transistor

e. Junction Flying Effect Transistor

· Apakah kepanjangan dari MOSFET

a. Metal Oxide Semiconductor Flying Effect Transistor

b. Mega Oxide Semicoductor Field Effect Transistor

c. Mega Oxide Standart Flying Effect Transistor

d. Metal Oxide Standart Field Effect Transistor

e. Metal Oxide Semiconductor Field Effect Transistor

· Apakah perbedaan JFET N-Chanel dengan JFET P-Chanel

a. Panahnya selalu berlawanan ke kiri maupun ke kanan

b. N-Chanel merupakan arus input dan P-Chanel merupakan Arus output

c. N-Chanel memiliki 2 panah dan P-Chanel 1 panah

d. Kecepatannya berbeda

e. Tidak ada perbedaan

Komentar

Posting Komentar